商机详情 -

频率综合器100kHz至40GHz

提到相位噪声性能,综合器设计师主要依靠100MHz恒温晶体振荡器(OCXO)技术。如今商用OCXO的输出在10KHz和100MHz偏移量达到-170至-176dBc/Hz(甚至更好)。如果频率综合器电路是“理想”的话,在10GHz可实现-130或-136dBc/Hz的相位噪声。虽然没有理想电路,所有当前的发展方向是力求理想。10MHz的OCXO的表现在较低的频率偏移(100Hz以下)时更好。此外,它的短期稳定性也优于100MHz振荡器。因此,综合器的设计通常将其输出到锁定10MHz参考频率。同样高频振荡器(如SAW和DRO)在100KHz及其以上频率偏移量上有更好的表现24-29。一个组合参考源包含几个彼此锁定的振荡器,可在任何频率偏移上实现比较低的相位噪声。通过使用蓝宝石谐振腔或者光学方法的高Q值振荡器可以进一步提高性能30-33。 AnaPico频率综合器分辨率低至0.00001Hz,输出高达40GHz。频率综合器100kHz至40GHz

可预置分频器在频率合成中,为了提高控制精度,鉴相器在低频下工作。而VCO电路输出频率是比较高的,为了提高整个环路的控制精度,离不开分频技术。分频器输出的信号送到相位比较器,和基准时钟信号进行相位比较。VCO电路在锁相环中比较重要,是频率合成及锁相环路的重要电路。它应满足这样一些特性:输出幅度稳定性要好,在整个VCO电路工作频带内均应满足此要求,否则会影响鉴相灵敏度;频率覆盖范围要满足要求且有余量;电压-频率变换特性的线性范围要宽。频率综合器100kHz至40GHz频率综合器可以将多个输入信号经过适当的处理后合成为一个输出频率信号。

频率综合器的工作原理分别是:直接模拟合成法、锁相环合成法和直接数字合成法。直接模拟合成法利用倍频、分频、混频及滤波,从单一或几个参数频率中产生多个所需的频率。该方法频率转换时间快(小于100ns),但是体积大、功耗大,已基本不被采用。锁相环合成法通过锁相环完成频率的加、减、乘、除运算。该方法结构简化、便于集成,且频谱纯度高,使用比较广,但存在高分辨率和快转换速度之间的矛盾,一般只能用于大步进频率合成技术中。

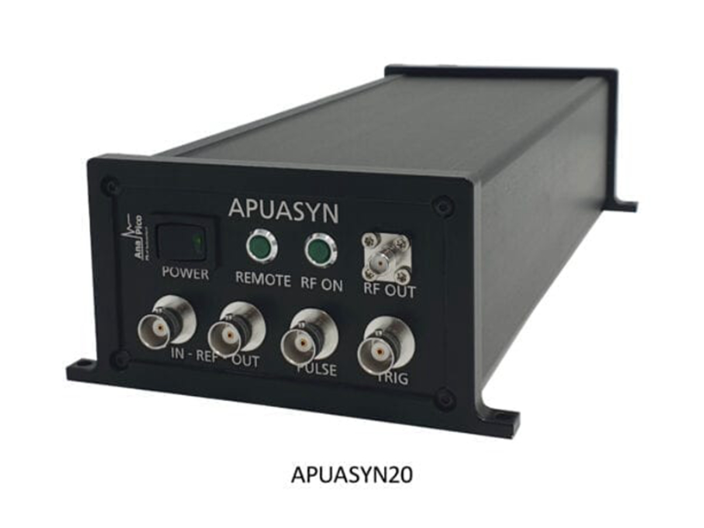

频率合成器的基本组成:采用锁相环(PLL)功能组成的频率合成器,每个频率合成环路一般包括:基准时钟振荡器、相位比较器、低通滤波器、压控振荡器和可预置分频器。频率合成器的基本工作过程:VCO频率的稳定过程和VCO频率的变频过程。将一个高稳定度和高精度的标准频率,经过功能电路的作用,产生具有同样稳定度和精确度的大量离散频率的技术称为频率合成技术。根据该原理组成的设备或仪器称为频率合成器(或频率综合器)。AnaPico频率综合器AnaPico频率综合器低相噪、大带宽、高分辨率、快速跳频。

随着微波通信技术的快速发展,对接收机的灵敏度要求越来越高,作为各类接收机的心脏,频率源需要为其提供高性能的本振信号,它的相位噪声指标成为制约接收机性能的关键因素之一。为了改善频率源的相噪,国内外很多公司和科研机构开展了很多这方面的研究,也提出了各种有效的方法。这些方法有的从构成锁相环的相位噪声来源直接分析,更多的从实现方式来分析,包括新型直接合成、DDS和锁相环芯片混合技术、自偏置、谐波混频、新型多级自谐波混频和级联式偏置、混频环等。AnaPico频率综合器分辨率低至0.00001Hz并具有良好的相噪和杂散指标。频率综合器100kHz至40GHz

AnaPico频率综合器可在1U机箱内输出4路相参但单独可控的高质量连续波和脉冲调制信号。频率综合器100kHz至40GHz

有很多技术可以降低小数分频的杂散。通常可以在分频系数变化的时候通过增加或减少鉴相器输出的电压来实现。另一种方法是使用一个允许更大的分频系数的多模分频器。在这种情况下,我们会得到大量的小幅度杂散。多模分频器往往和Delta-Sigma调制器一起使用,产生随机频率杂散并将它们推向更高的偏移频率,使其可以通过回路滤波器过滤掉。尽管存在各种改进的技术,小数分频技术的主要缺点是由小数划分机制导致的相位误差过量产生的大量杂散电平。频率综合器100kHz至40GHz